- Auteur Lynn Donovan donovan@answers-technology.com.

- Public 2023-12-15 23:51.

- Laatst gewijzigd 2025-01-22 17:35.

VHDL en Verilog worden beschouwd als digitale ontwerptalen voor algemene doeleinden, terwijl SystemVerilog een verbeterde versie van Verilog . VHDL heeft wortels in de Ada programmeertaal in zowel concept als syntaxis, terwijl Verilog's wortels kunnen worden teruggevoerd op een vroege HDL genaamd Hilo en de C-programmeertaal.

Mensen vragen ook, wat is beter VHDL of Verilog?

VHDL is uitgebreider dan Verilog en het heeft ook een niet-C-achtige syntaxis. Met VHDL , heb je een grotere kans om meer regels code te schrijven. Verilog heeft een beter greep op hardwaremodellering, maar heeft een lager niveau van programmeerconstructies. Verilog is niet zo uitgebreid als VHDL dus daarom is het compacter.

En wat is het nut van Verilog? Verilog is een hardwarebeschrijvingstaal; een tekstueel formaat voor het beschrijven van elektronische schakelingen en systemen. Toegepast op elektronisch ontwerp, Verilog is bedoeld om te worden gebruikt voor verificatie door middel van simulatie, voor timinganalyse, voor testanalyse (testbaarheidsanalyse en foutbeoordeling) en voor logische synthese.

Wat is op deze manier het verschil tussen Verilog en SystemVerilog?

de belangrijkste verschil tussen Verilog en SystemVerilog is dat Verilog is een hardwarebeschrijvingstaal, terwijl SysteemVerilog is een hardwarebeschrijving en hardwareverificatietaal gebaseerd op: Verilog . In het kort, SysteemVerilog is een verbeterde versie van Verilog met extra functies.

Wat is VHDL in VLSI?

VLSI Ontwerp - VHDL Inleiding. Advertenties. VHDL staat voor zeer snelle hardwarebeschrijvingstaal voor geïntegreerde schakelingen. Het is een programmeertaal die wordt gebruikt om een digitaal systeem te modelleren door middel van dataflow, gedrags- en structurele modelleringsstijlen.

Aanbevolen:

Wat is het verschil tussen de toestand van het hele rapport en het gedeeltelijke rapport?

Voor niet-gerelateerde items in een lijst (zoals in de experimenten van Nieuwenstein & Potter, 2006) wordt het hele rapport beïnvloed door het totale aantal items in een reeks, terwijl een gedeeltelijk rapport slechts minimaal wordt beïnvloed door het totale aantal items, als er maar twee moeten worden gemeld

Wat is het verschil tussen het geschatte uitvoeringsplan en het daadwerkelijke uitvoeringsplan?

2 antwoorden. Het geschatte uitvoeringsplan wordt uitsluitend gegenereerd op basis van de statistieken die SQL Server heeft - zonder de query daadwerkelijk uit te voeren. Het daadwerkelijke uitvoeringsplan is precies dat - het daadwerkelijke uitvoeringsplan dat werd gebruikt bij het daadwerkelijk uitvoeren van de query

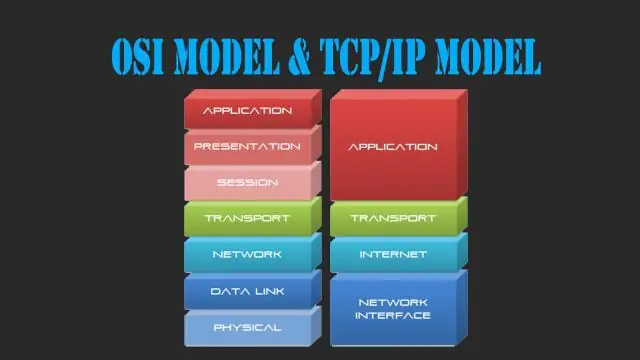

Wat is het verschil tussen het OSI-model en het TCP IP-model?

1. OSI is een generieke, protocolonafhankelijke standaard die fungeert als communicatiegateway tussen het netwerk en de eindgebruiker. Het TCP/IP-model is gebaseerd op standaardprotocollen waarrond internet zich heeft ontwikkeld. Het is een communicatieprotocol waarmee hosts via een netwerk kunnen worden aangesloten

Wat is het verschil tussen het insluiten van een diagram en het koppelen van een diagram?

Wat is het verschil tussen het insluiten van een diagram en het koppelen van een diagram? een ingesloten grafiek is statisch en verandert niet automatisch als het werkblad dat wel doet. een gekoppelde grafiek wordt automatisch bijgewerkt wanneer de grafiek wordt bijgewerkt in Excel

Wat is het verschil tussen het klembord en het Office-klembord?

Het Office Klembord kan de laatste 24 gekopieerde items bewaren. Het Office-klembord verzamelt ook een lijst met gekopieerde items uit meerdere documenten in elk Office-programma die u als groep in een ander Office-programmadocument kunt plakken